We all know that time and frequency synchronization have always been important for mobile networks. Especially in 5G networks, high precision time synchronization within microseconds will be required. 5G will not only provide personal mobile service, but also massive machine type communications (MTC) and latency/reliability critical services. These critical services require time division duplex (TDD) communications with tight time synchronizationbetter than +/- 1.5 microseconds network-wide. GNSS provides tight time synchronization, but this is an expensive solution to deploy across multiple locations. Alternatively, the Ethernet-based IEEE 1588 PTP timing protocol is designed to deliver high accuracy timing packets to the end devices through hardware time stamping of packets and accumulated delay calculations. This is a less expensive solution compared to GNSS.

To support PTP/IEEE 1588, Broadcom introduced a solution called BroadPTP™ which is designed for Broadcom StrataDNX™ and StrataXGS™ switching chips. Some customers prefer to reuse their own PTP stack along with an FPGA-based Time Stamp Counter (TSC) with the Broadcom chip internal TSC. Another use case is IEEE 1588 PTP timestamp synchronization on chassis-based products where the timestamp must be synchronized across all the card slots. In the latter two cases Broadcom has a proprietary solution known as BroadSync™.

1. What is BroadSync? Infrastructure introduction

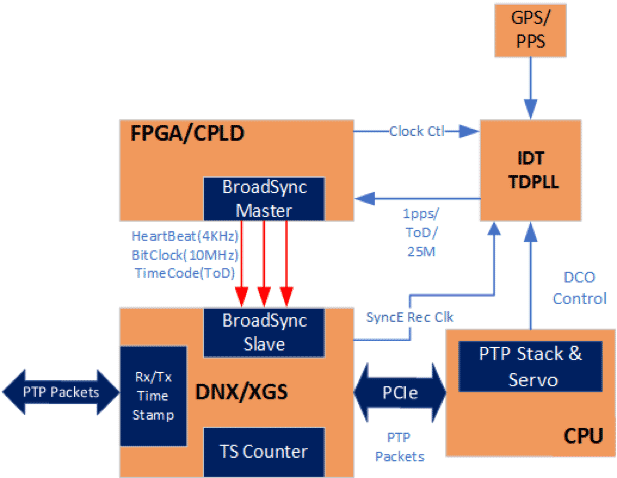

BroadSync is a Broadcom software-firmware that runs on a StrataDNX/XGS internal ARM processor and it synchronizes the time-based events between a BroadSync-Master (source) and BroadSync-Slaves (sinks). Synchronization is achieved via three signals on the device and uses proprietary logic in the device, as shown in the diagram below.

The FPGA takes on the role of BroadSync master and drives BroadSync signals to Broadcom DNX/XGS chips. The Broadcom DNX/XGS chips take the BroadSync slave role to receive signals and interpret them to achieve a precise alignment with the Time of Day (TOD) values in the FPGA.

2. Mechanism

The BroadSync interface consists of three bi-directional signals: HeartBeat, BitClock, and TimeCode.These signals are output-only in BroadSync Master mode or input-only in BroadSync Slave mode.

HeartBeat

The heartbeat signal runs continuously at a recommended frequency of 4KHz and is synchronous with the BitClock. The BroadSync master timestamps the rising edge of its heartbeat input signal and the BroadSync slave interprets the timestamps to establish the correct phase or frequency of heartbeat output signals.

BitClock

The higher speed BitClock signal runs at 10MHz and is used to shift the TimeCode values out of the master device. On a slave device the BitClock receives the clock signal and uses it to shift timeCode value from an external timing source.

TimeCode

The 97-bit long TimeCode value is shifted into, or out of, the device serially once per heartbeat period. The timeCode value consists of a lock indication, the time-of-day value for the current heartbeat period and an indication of the quality or reliability of the time value.

With the TOD synchronization between the FPGA and Broadcom chip, a timestamp will be attached to the Broadcom ingress packet header and sent to the CPU. In the egress direction, the correct egress timestamp will also be written into the PTP packet by the Broadcom chip.

3. BroadSync Accuracy Measurements

One of the most critical BroadSync requirements is its accuracy measurement. The BroadSync accuracy measurement is done using an external 1PPS (pulse per second) signal using a GPIO pin.

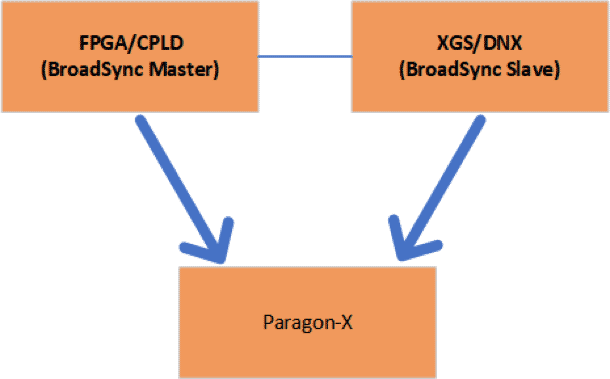

As shown in the diagram below, the BroadSync-master and slave must have the 1PPS-out connection and they must be connected to a measurement device such as Paragon-X to count the difference between the two 1PPS signals.

4. BroadSync timing interface use cases

In a grandmaster timing scenario, the PTP grandmaster clock device receives the clock from an external timing source such as a GPS or an atomic clock. Consequently, the BroadSync interface is an input for a grandmaster clock, which obtains timing information from an external clock source. In this scenario, the device with the Broadcom chip along with the BroadSync timing interface can act as PTP Grandmaster.

In an external PTP stack scenario, BroadPTP software combines a feature rich PTP stack with a highly flexible servo to provide an integrated and scalable PTP/IEEE 1588 solution. BroadPTP is not supported on all Broadcom switching devices and some customers prefer to reuse their own proprietary PTP stack. In this case, the time stamper in Broadcom switching devices must be synchronized using a BroadSync timing interface with an external host CPU based PTP stack.

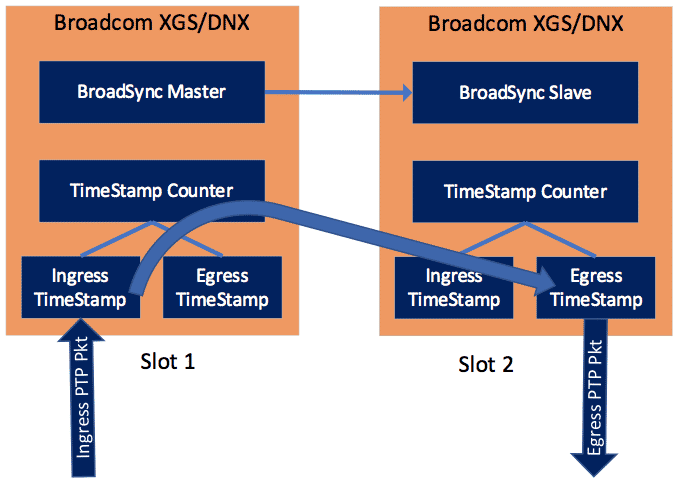

In a chassis system synchronization scenario, the PTP stack and servo run on a timing card, and each line card must synchronize its timestamp counter using a BroadSync timing interface. As shown in diagram below, the IEEE 1588 PTP traffic may ingress into one line card and egress from another line card, thus the timestamp counters must be synchronized between different slots.

5. Summary

BroadSync integration with an external IEEE 1588 PTP stack solution requires deep knowledge of BroadSync interfaces and handling of timing signals in hardware. IP Infusion has been helping several customers in integrating the BroadSync solution into their proprietary IEEE 1588 PTP stack. With this expertise IP Infusion can help customers speed up product development.